# Lecture 8 SystemVerilog HDL

Peter Cheung Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/EE2\_CAS/E-mail: p.cheung@imperial.ac.uk

## **Lecture Objectives**

- By the end of this lecture, you should understand:

- The basic structure of a module specified in SystemVerilog HDL

- Commonly used syntax of SystemVerilog HDL

- Continuous vs Procedural Assignments

- always block in SystemVerilog and sensitivity list

- The use of arithmetic and logic operations in SystemVerilog

- The danger of incomplete specification

- How to specify clocked circuits

- Differences between blocking and nonblocking assignments

#### Schematic vs HDL

#### **Schematic**

- Good for multiple data flow

- ✓ Give overview picture

- Relate directly to hardware

- Don't need good programming skills

- High information density

- Easy back annotations

- Useful for mixed analogue/digital

- × Not good for algorithms

- × Not good for datapaths

- Poor interface to optimiser

- × Poor interface to synthesis software

- × Difficult to reuse

- × Difficult to parameterise

#### **HDL**

- Flexible & parameterisable

- Excellent input to optimisation & synthesis

- ✓ Direct mapping to algorithms

- Excellent for datapaths

- Easy to handle electronically (only needing a text editor)

- × Serial representation

- × May not show overall picture

- × Need good programming skills

- × Divorce from physical hardware

# SystemVerilog HDL

- Similar to C language to describe/specify hardware

- Description can be at different levels:

- Behavioural level

- Register-Transfer Level (RTL)

- Gate Level

- Not only a specification language, also with associated simulation environment

- Easier to learn and "lighter weight" than its competition: VHDL

- Very popular with chip designers

- For this lecture, we will:

- Learn through examples and practical exercises

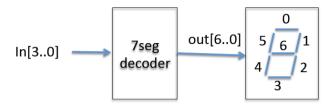

- ☐ Use examples: e.g. 2-to-1 multiplexer and 7 segment decoder

#### **HDL** to Gates

#### Simulation

- Inputs applied to circuit

- Outputs checked for correctness

- Millions of dollars saved by debugging in simulation instead of hardware

#### Synthesis

Transforms HDL code into a netlist describing the hardware (i.e., a list of gates and the wires connecting them)

#### Physical design

Placement, routing, chip layout, ..... – not considered in this module

#### **IMPORTANT:**

When using an HDL, think of the **hardware** the HDL should produce, then write the appropriate idiom that implies that hardware.

Beware of treating HDL like software and coding without thinking of the hardware.

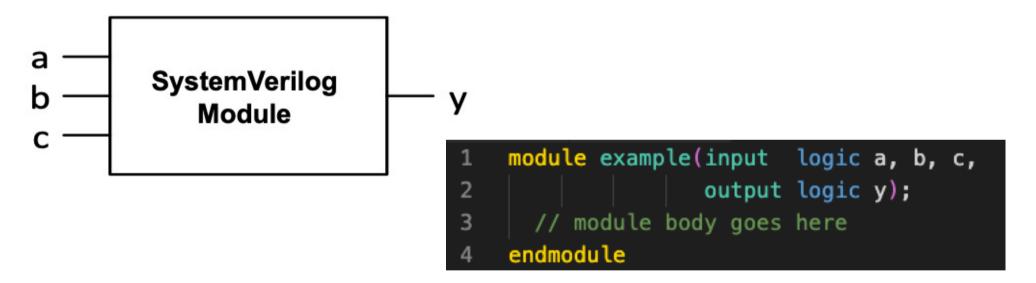

# SystemVerilog: Module Declaration

- **Two types of Modules:**

- Behavioral: describe what a module does

- Structural: describe how it is built from simpler modules

- \* module/endmodule: required to begin/end module

- \* example: name of the module

# System Verilog: Behavioural Description

Based on: "Digital Design and Computer Architecture (RISC-V Edition)" by Sarah Harris and David Harris (H&H),

simulation

| Now:<br>800 ns |   | 0 ns 160 320 ns 480 640 ns 800 |

|----------------|---|--------------------------------|

| <b>∛l</b> a    | 0 |                                |

| <b>∛ll</b> b   | 0 |                                |

| <b>∭</b> c     | 0 |                                |

| <b>₹</b> У     | 0 |                                |

# **System Verilog: Syntax**

- Case sensitive

- e.g.: reset and Reset are not the same signal.

- No names that start with numbers

- e.g.: 2mux is an invalid name

- Whitespace ignored

- **Comments:**

- // single line comment

- /\* multiline

- comment \*/

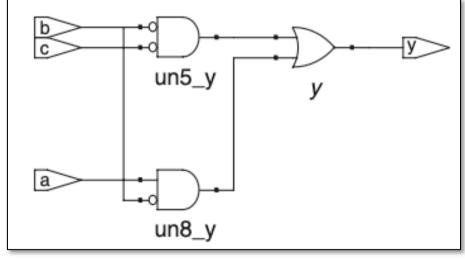

# System Verilog: Structural Description

#### Behavioural

#### Structural

# **System Verilog: Bitwise Operators**

Based on: "Digital Design and Computer Architecture (RISC-V Edition)" by Sarah Harris and David Harris (H&H),

v3[3:0]

[3:0] y4[3:0]

[3:0] y1[3:0]

v5[3:0]

v2[3:0]

y4[3:0]

y5[3:0]

y1[3:0]

y2[3:0]

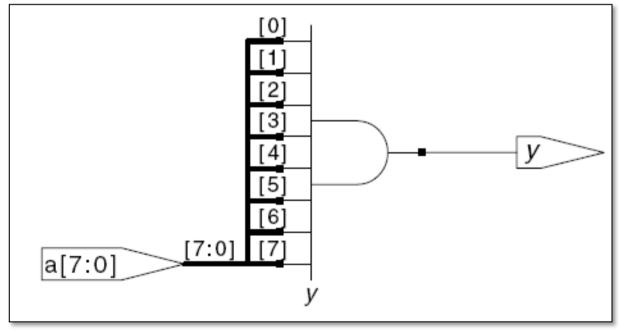

# SysytemVerilog: Reduction Operators

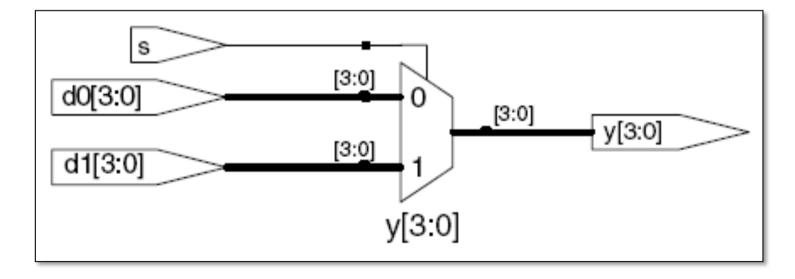

# System Verilog: Conditional Assignment

# **System Verilog: Internal Signals**

```

module fulladder(input logic a, b, cin,

output logic s, cout);

logic p, g; // internal nodes

assign p = a ^ b;

assign g = a \& b;

assign s = p ^ cin;

assign cout = g | (p & cin);

endmodule

din

```

Based on: "Digital Design and Computer Architecture (RISC-V Edition)" by Sarah Harris and David Harris (H&H),

cout

un1\_cout

cout

# System Verilog: Precedence of operators

#### **Highest**

| ~            | NOT              |

|--------------|------------------|

| *, /, %      | mult, div, mod   |

| +, -         | add, sub         |

| <<, >>       | shift            |

| <<<, >>>     | arithmetic shift |

| <, <=, >, >= | comparison       |

| ==, !=       | equal, not equal |

| &, ~&        | AND, NAND        |

| ^, ~^        | XOR, XNOR        |

| , ~          | OR, NOR          |

| ?:           | ternary operator |

#### Lowest

# **System Verilog: Number Format**

Format: N'Bvalue

N = number of bits, B = base

N'B is optional but recommended (default is decimal)

| Number         | # Bits  | Base        | Decimal<br>Equivalent | Stored    |

|----------------|---------|-------------|-----------------------|-----------|

| 3'b101         | 3       | binary      | 5                     | 101       |

| <b>'</b> b11   | unsized | binary      | 3                     | 000011    |

| 8 <b>'</b> b11 | 8       | binary      | 3                     | 00000011  |

| 8'b1010_1011   | 8       | binary      | 171                   | 10101011  |

| 3'd6           | 3       | decimal     | 6                     | 110       |

| 6 <b>'</b> 042 | 6       | octal       | 34                    | 100010    |

| 8'hAB          | 8       | hexadecimal | 171                   | 10101011  |

| 42             | Unsized | decimal     | 42                    | 000101010 |

# System Verilog: Bit Manipulations (1)

```

assign y = {a[2:1], {3{b[0]}}, a[0], 6'b100_010};

```

❖ If y is a 12-bit signal, the above statement produces:

```

y = a[2] a[1] b[0] b[0] b[0] a[0] 1 0 0 0 1 0

```

Underscores (\_) are used for formatting only to make it easier to read. System Verilog ignores them.

# System Verilog: Bit Manipulations (2)

```

module mux2_8(input logic [7:0] d0, d1,

input logic

output logic [7:0] y);

mux2 lsbmux(d0[3:0], d1[3:0], s, y[3:0]);

mux2 msbmux(d0[7:4], d1[7:4], s, y[7:4]);

endmodule

mux2

[7:0]

[3:0]

d0[7:0]

d0[3:0]

v[3:0]

y[7:0]

[3:0]

[7:0]

d1[3:0]

d1[7:0]

Isbmux

mux2

[7:4]

d0[3:0]

v[3:0]

[7:4]

d1[3:0]

msbmux

```

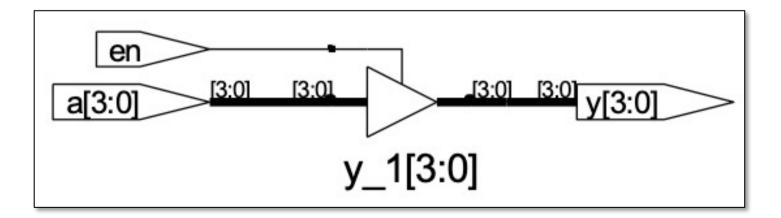

# System Verilog: Floating Output Z

## Note that Verilator does not handle floating output Z

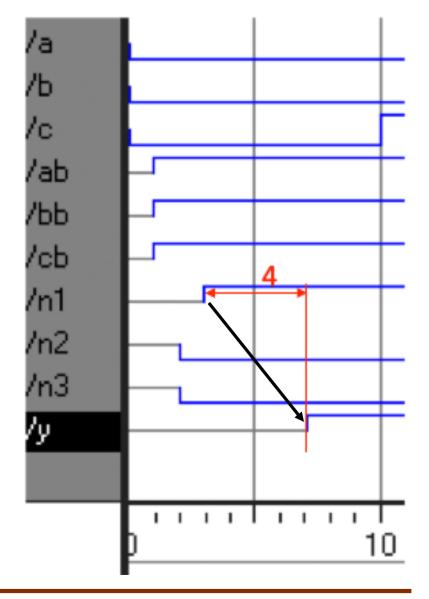

# **System Verilog: Delays**

- Delays are for simulation only! They do not determine the delay of your hardware.

- Verilator similator ignores delays it is cycle accurate without timing.

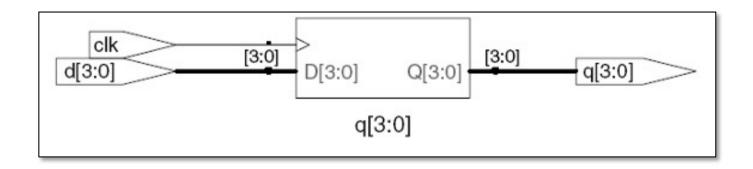

# System Verilog: Sequential Logic

- System Verilog uses idioms (or special keywords or groups of words) to describe latches, flip-flops and FSMs

- Other coding styles may simulate correctly but produce incorrect hardware

- GENERAL STRUCTURE:

```

always @(sensitivity list)

statement;

```

Whenever the event in sensitivity list occurs, statement is executed

# System Verilog: D Flip-Flop

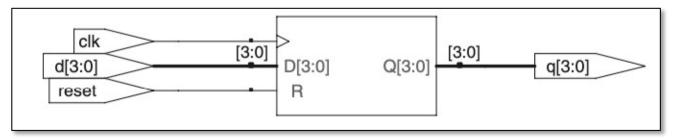

# System Verilog: Resettable D Flip-Flop

## Asynchronous reset

# Synchronous reset

# **Combinational Logic using always**

```

// combinational logic using an always statement

module gates(input logic [3:0] a, b,

output logic [3:0] y1, y2, y3, y4, y5);

always_comb // need begin/end because there is

// more than one statement in always

begin

y1 = a \& b; // AND

y2 = a | b; // OR

y3 = a ^ b; // XOR

y4 = \sim (a \& b); // NAND

y5 = \sim (a | b); // NOR

end

endmodule

```

This hardware could be described with assign statements using fewer lines of code, so it's better to use assign statements in this case.

## Putting everything together – 7 seg decoder

#### In3: in2

| out6 | 00 | 01 | 11 | 10 |

|------|----|----|----|----|

| 00   | 1  | 0  | 1  | 0  |

| 01   | 1  | 0  | 0  | 0  |

| 11   | 0  | 1  | 0  | 0  |

| 10   | 0  | 0  | 0  | 0  |

| in[30] | out[6:0] | Digit |

|--------|----------|-------|

| 0000   | 1000000  | 0     |

| 0001   | 1111001  | 1     |

| 0010   | 0100100  | 2     |

| 0011   | 0110000  | 3     |

| 0100   | 0011001  | 4     |

| 0101   | 0010010  | 5     |

| 0110   | 0000010  | 6     |

| 0111   | 1111000  | 7     |

|        |          |       |

| in[30] | out[6:0] | Digit |

|--------|----------|-------|

| 1000   | 0000000  | 8     |

| 1001   | 0010000  | 9     |

| 1010   | 0001000  | A     |

| 1011   | 0000011  | Ь     |

| 1100   | 1000110  | Ε     |

| 1101   | 0100001  | d     |

| 1110   | 0000110  | Ε     |

| 1111   | 0001110  | F     |

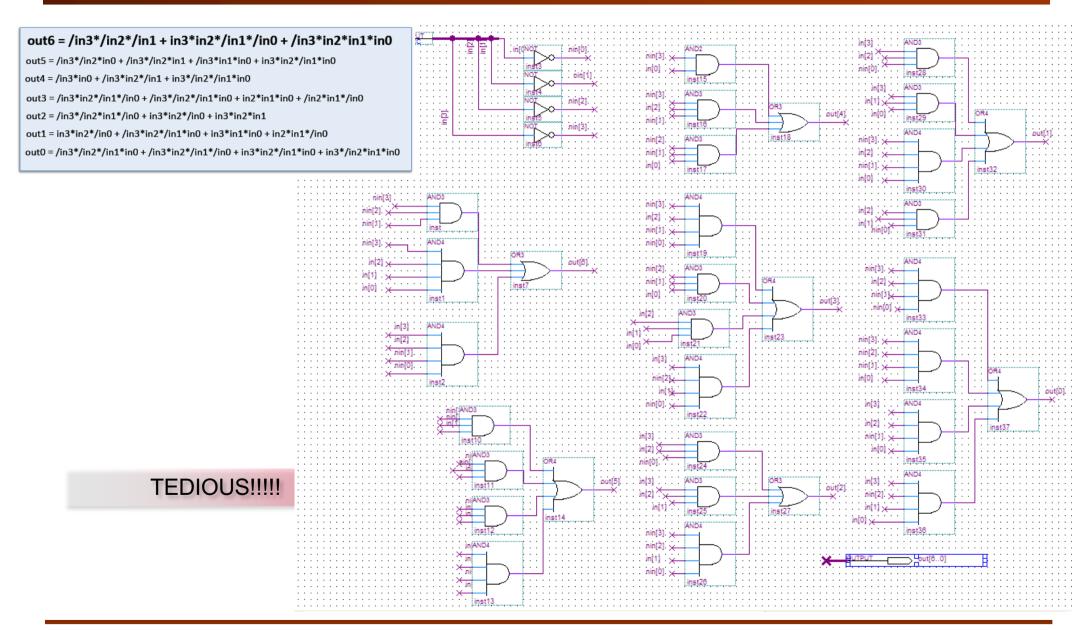

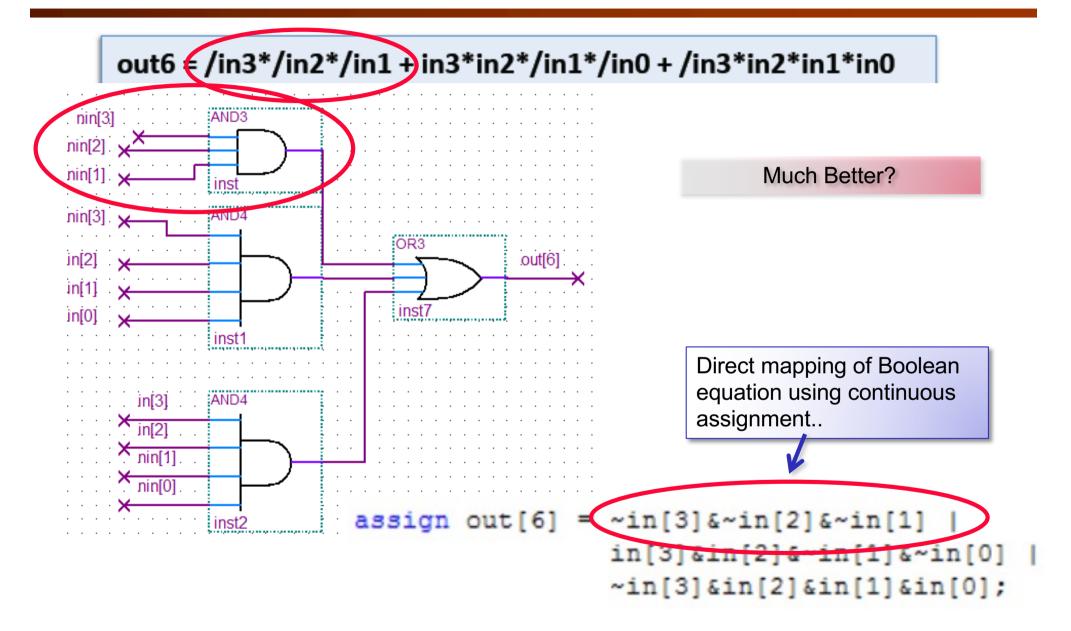

#### out6 = /in3\*/in2\*/in1 + in3\*in2\*/in1\*/in0 + /in3\*in2\*in1\*in0

out5 = /in3\*/in2\*in0 + /in3\*/in2\*in1 + /in3\*in1\*in0 + in3\*in2\*/in1\*in0

out4 = /in3\*in0 + /in3\*in2\*/in1 + in3\*/in2\*/in1\*in0

out3 = /in3\*in2\*/in1\*/in0 + /in3\*/in2\*/in1\*in0 + in2\*in1\*in0 + /in2\*in1\*/in0

out2 = /in3\*/in2\*in1\*/in0 + in3\*in2\*/in0 + in3\*in2\*in1

out1 = in3\*in2\*/in0 + /in3\*in2\*/in1\*in0 + in3\*in1\*in0 + in2\*in1\*/in0

out0 = /in3\*/in2\*/in1\*in0 + /in3\*in2\*/in1\*/in0 + in3\*in2\*/in1\*in0 + in3\*/in2\*in1\*in0

# **Method 1: Schematic Entry Implementation**

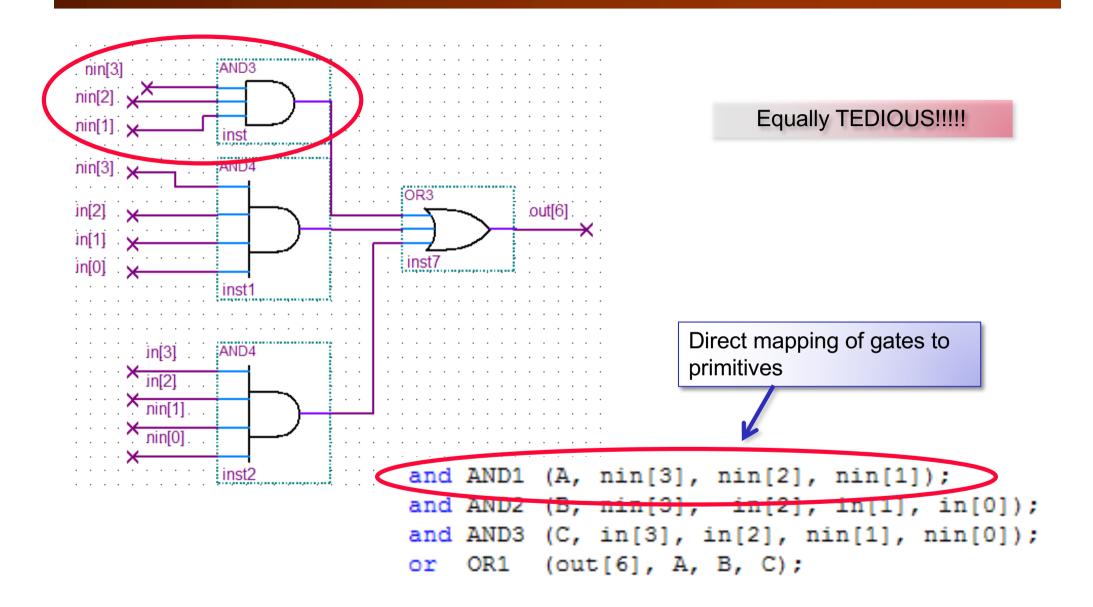

# Method 2: Use primitive gates in Verilog

## Method 3: Use continuous assignment in Verilog

#### module & endmodule

sandwich the content of this hardware module

# Hexto7seg.v (in Verilog)

```

good header helps

Module name: hex to 7seq

documenting your code

Function: convert 4-bit hex value to drive 7 segment display

output is low active

specify interface to this

Creator: Peter Cheung

module as viewed from

Version: 1.0

outside

specify a 7-bit output bus,

22 Oct 2011

Date:

out[6] ... out[0]

module hex to 7seg

(out, in);

declaration of

input and output

// low-active output to drive 7 segment display

output

[6:0]

// 4-bit binary input of a hexademical number

input

[3:0]

in:

ports

assign out[6] = ~in[3]&~in[2]&~in[1] | in[3]&in[2]&~in[1]&~in[0] |

~in[3]&in[2]&in[1]&in[0];

assign out[5] = ~in[3]&~in[2]&in[0] | ~in[3]&~in[2]&in[1] |

~in[3]&in[1]&in[0] | in[3]&in[2]&~in[1]&in[0];

assign out[4] - in[3]&in[0] | ~in[3]&in[2]&~in[1] | in[3]&~in[2]&~in[1]&in[0];

assign out[3] = \min[3] \& \inf[2] \& \inf[1] \& \min[0] | \min[3] \& \min[2] \& \min[1] \& \inf[0] |

in[2]&in[1]&in[0] | ~in[2]&in[1]&~in[0];

assign out [2] = \sim in[3] \& \sim in[2] \& in[1] \& \sim in[0] | in[3] \& in[2] \& \sim in[0]

assign used to specify

in[3]&in[2]&in[1];

combinational circuit

assign out[1] = in[3] \& in[2] \& \sim in[0] | \sim in[3] \& in[2] \& \sim in[1] \& in[0]

in[3]&in[1]&in[0] | in[2]&in[1]&~in[0];

assign out[0] = ~in[3]&~in[2]&~in[1]&in[0] | ~in[3]&in[2]&~in[1]&~in[0] |

in[3]&in[2]&~in[1]&in[0] | in[3]&~in[2]&in[1]&in[0];

endmodule

```

#### Method 4: Power of behavoural abstraction

```

module hexto7seq

output logic [6:0] out, // low-active

input logic [3:0] in  // 4-bit bina

always_comb

BEAUTIFUL !!!

case (in)

4'h0: out = 7'b1000000:

4'h1: out = 7'b1111001;

// -- 0 -

4'h2: out = 7'b0100100;

// 5

4'h3: out = 7'b0110000;

4'h4: out = 7'b0011001:

// -- 6 -

4'h5: out = 7'b0010010:

4'h6: out = 7'b0000010;

4'h7: out = 7'b1111000;

// 4

4'h8: out = 7'b0000000;

4'h9: out = 7'b0011000:

// -- 3 -

4'ha: out = 7'b0001000;

4'hb: out = 7'b0000011;

4'hc: out = 7'b1000110;

4'hd: out = 7'b0100001;

4'he: out = 7'b0000110;

Direct mapping of truth

4'hf: out = 7'b0001110;

table to case statement

default: out = 7'b0000000; // de1

Close to specification,

endcase

not implementation

endmodule

```

| in[30] | out[6:0] | Digit |

|--------|----------|-------|

| 0000   | 1000000  | 0     |

| 0001   | 1111001  | 1     |

| 0010   | 0100100  | 2     |

| 0011   | 0110000  | 3     |

| 0100   | 0011001  | 4     |

| 0101   | 0010010  | 5     |

| 0110   | 0000010  | 6     |

| 0111   | 1111000  | 7     |

| 1000   | 0000000  | 8     |

| 1001   | 0010000  | 9     |

| 1010   | 0001000  | R     |

| 1011   | 0000011  | Ь     |

| 1100   | 1000110  | E     |

| 1101   | 0100001  | d     |

| 1110   | 0000110  | Ε     |

| 1111   | 0001110  | F     |

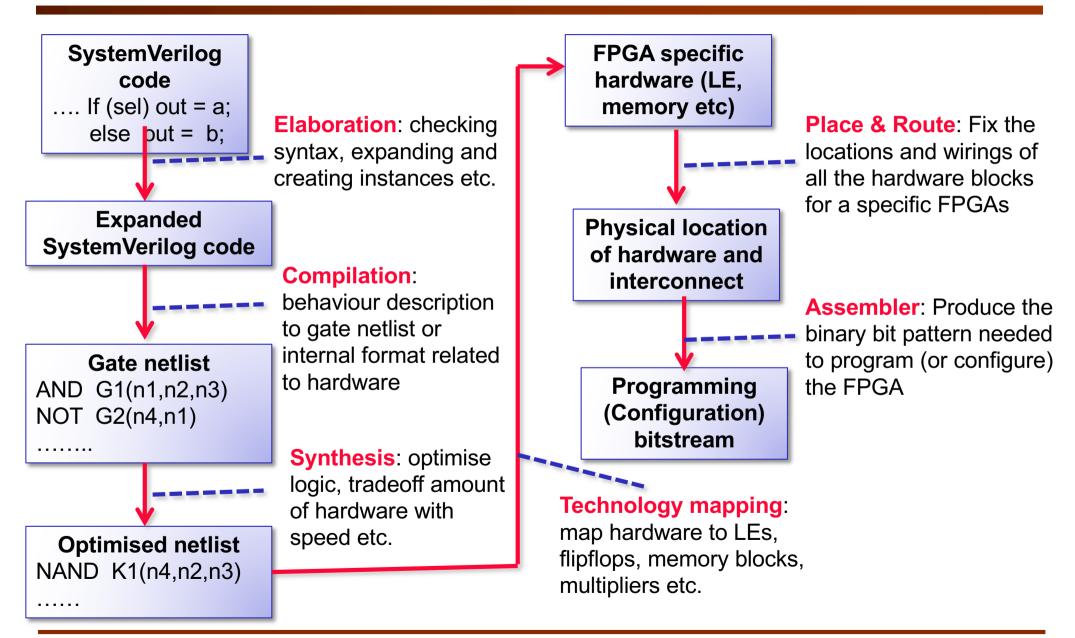

# From SystemVerilog code to FPGA hardware

# Power of SystemVerilog: Integer Arithmetic

Arithmetic operations make computation easy:

```

module add32 (

input logic [31:0] a,

input logic [31:0] b,

output logic [31:0] sum

);

assign sum = a + b;

endmodule

```

Here is a 32-bit adder with carry-in and carry-out:

```

module add32_carry (

input logic [31:0] a,

input logic [31:0] b,

input logic cin,

output logic [31:0] sum,

output logic cout

);

assign {cout, sum} = a + b + cin;

endmodule

```

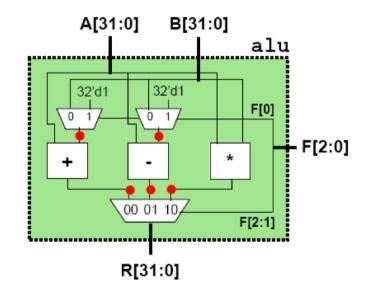

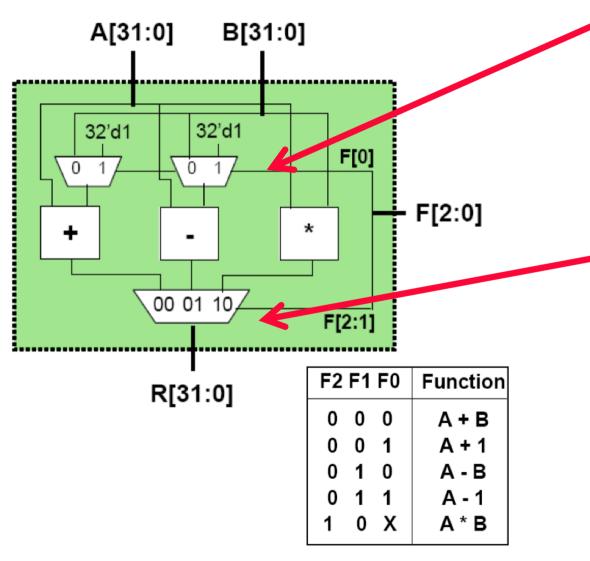

# A larger example – 32-bit ALU in SV

Here is an 32-bit ALU with 5 simple instructions:

```

module mux2to1 (

input logic [31:0] i0,

input logic [31:0] i1,

input logic sel,

output logic [31:0] out

);

assign out = sel ? i1 : i0;

endmodule

```

```

module mux3to1 (

input logic [31:0]

i0,

input logic [31:0]

i1,

input logic [31:0]

i3,

input logic [1:0]

sel,

output logic [31:0]

out

);

always_comb

case (sel)

2'b00:

out = i0;

2'b01:

out = i1;

2'b10: out = i2;

default: out = 32'bx;

endcase

endmodule

```

#### The arithmetic modules

module mul16 ( Here is an 32-bit ALU with 5 simple instructions: input logic [15:0] i0. B[31:0] A[31:0] input logic [15:0] i1, output logic [31:0] pro assign prod = i0 \* i1; 32'd1 32'd1 endmodule F[0] 0 1 module sub32 ( F[2:0] input logic [31:0] i0, input logic [31:0] i1, output logic [31:0] diff 00 01 104 ); F[2:1] assign diff = i0 - i1; endmodule R[31:0] module add32 ( input logic [31:0] i0, input logic [31:0] i1, output logic [31:0] sum assign sum = i0 + i1; endmodule

## Top-level module – putting them together

Given submodules:

```

module mux2to1 (i0, i1, sel, out);

module mux3to1 (i0, i1, i2, sel, out);

module add32 (i0, i1, sum);

module sub32 (i0, i1, diff);

module mul16 (i0, i1, prod);

```

```

module alu (

input logic [31:0]

a,

input logic [31:0]

input logic [2:0]

f.

output logic [31:0]

);

logic [32:0]

addmux out, submux out;

logic [32:0]

add out, sub out, mul out;

mux2to1 adder_mux (b, 32'd1, f[0], addmux_out);

mux2to1 sub_mux (b, 32'd1, f[0], submux_out);

add32

our adder (a, addmux out, add out);

sub32 out sub (a, submux out, sub out);

mul16

our mult (a[15:0], b[15:0], mul out);

mux3to1 output_mux(add_out, sub_out, mul_out, f[2:1], r);

endmodule

```